您可能听说过Vaxel零,在Windows PC上运行的FPGA配置/操作自动化解决方案。VAXEL零是由一组经验丰富的RTL设计验证工程师开发的,他们想利用FPGA来加速模拟和测试过程,但不想被FPGA通常需要的那些繁琐的配置和操作任务所打扰。

vaxel零的单一最大值是其生产力优化。它允许您最大限度地减少您花费的时间,配置和操作我们的Zynq板Zybo Z7.和Eclypse Z7。因此,它最大限度地提高了对逻辑实际设计验证和测试的时间。

以下是VAXEL ZERO的六个主要特征。

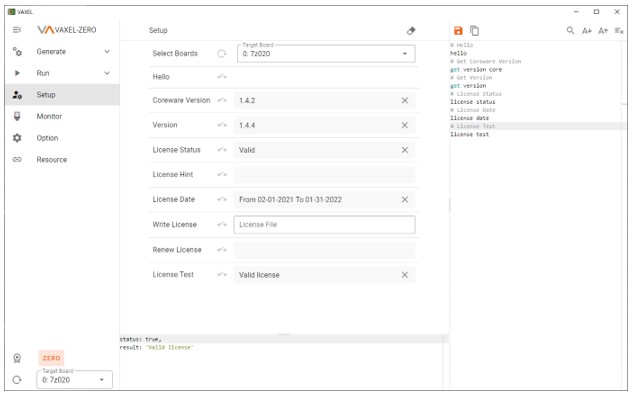

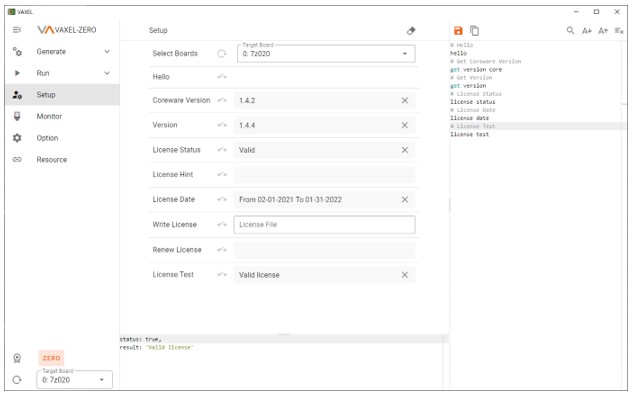

- 使用VAXEL Zero(Windows PC)轻松设置Zynq Loars(Windows PC):后下载并安装VAXEL ZERO包在您的Windows PC上,在Zynq Board上设置VAXEL零,需要零效率。使用标准USB电缆将Zynq Board连接到Windows PC并在Zynq Lobar开关时,一旦将Zynq Board连接到Windows PC,即可在设置屏幕上可见。

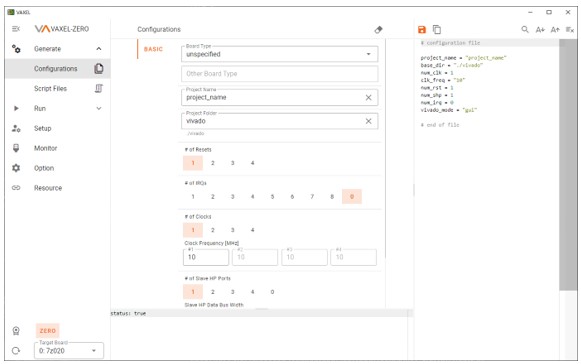

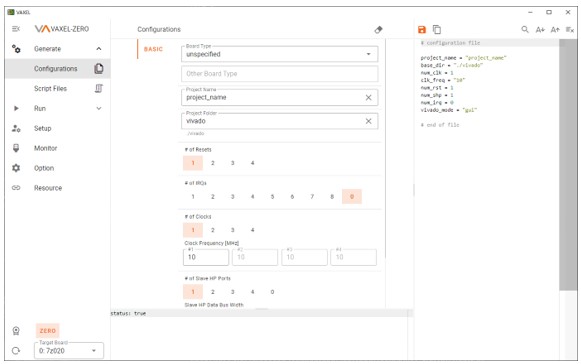

- 轻松准备和配置Zynq处理器,如时钟和总线:虽然所有工程师希望专注于使用FPGA的RTL设计的验证和测试,但通常意味着它们必须分配令人沮丧的时间来准备和配置船上FPGA上的处理器,例如时钟和总线。如下所示,VAXEL ZERO提供了一种工具,它允许您通过填写GUI的一些参数来完成Zynq处理器配置的工具。

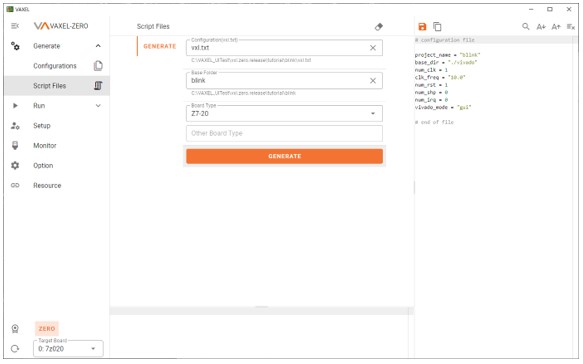

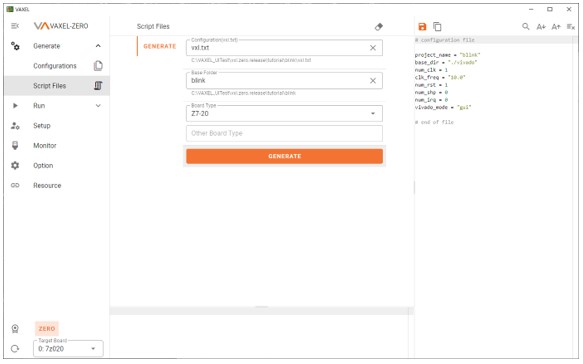

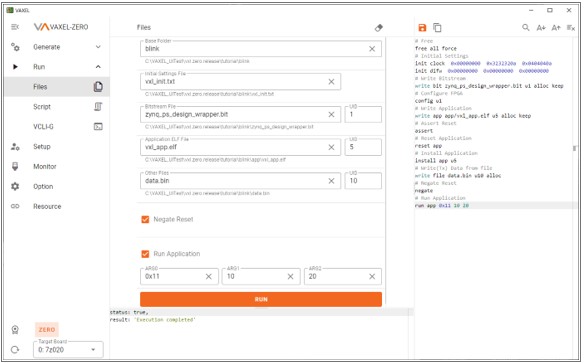

- 轻松生成PS并将比特流发送给可编程逻辑:一旦zynq处理器配置完成,您就可以使用vaxel零UI生成Zynq处理器系统(PS)部分。当PS部分已准备就绪时,您可以将其与位于可编程逻辑(PL)的比特流包装并将其传输到Zynq板,如下屏幕截图所示。

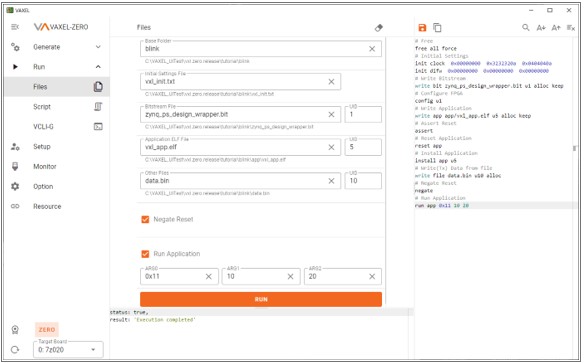

- 您的逻辑控制程序和应用程序(C代码)将自动上传到其中一个ARM处理器:除了将C应用程序上传到Zynq板上的一个ARM处理器之外,Vaxel Zax Zaxel还提供了一个很好的GUI,允许您从Windows PC操作应用程序,而只是发送参数。

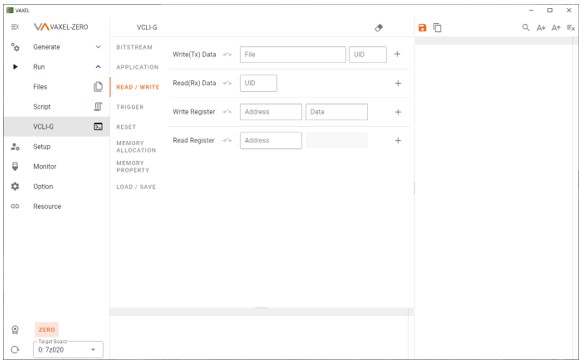

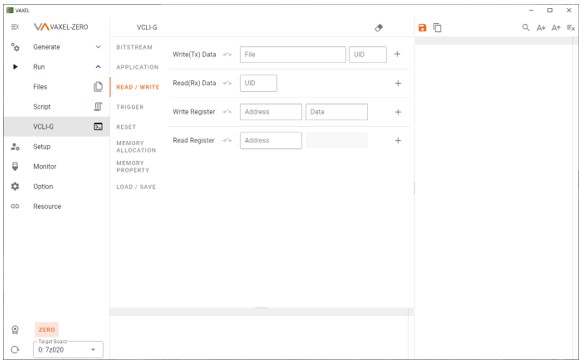

- VCLI为您提供了管理FPGA内部资源的命令行功能。初始调试是非常高效的:VCLI是一个专有的命令行接口。它提供了一组用于管理FPGA资源的简单和直观的命令。

- VAXEL Zero现有的Python库允许您构建和运行在Python中编写的一些复杂的测试场景:如今,Python是全球使用最广泛的编程语言之一。我们决定用一个Python库装备vaxel Zero,该库允许从Windows PC上的FPGA上执行任何Python程序。

----- Python中的示例代码-----

def test_one(测试):

打印(' - 测试#{0} - '。格式(test [0]))

#明确资源

清除()

#获取PL基地地址

pladdr = vxl.get_pladdr ()

#传输测试数据

write_file_to_uid(uid_input_img,test [3],0)

如果LEN(测试[4])> 0:

write_file_to_uid(UID_LUT_R, test[4], pladdr+REG_IMGFLT_LUT_R)

如果len(test[5]) > 0:

write_file_to_uid(UID_LUT_G, test[5], pladdr+REG_IMGFLT_LUT_G)

如果LEN(测试[6])> 0:

write_file_to_uid(uid_lut_b,test [6],pladdr + reg_imgflt_lut_b)

#运行应用程序

print('运行应用程序')

Vxl.run_app(测试[1],测试[2],0)

#发送触发器完成应用程序

vxl.set_trig(trig_exit_app,1)#提前触发

#等待完成信号

而(vxl.stat_app()[0] & vxl。Vxl_stat_exit) == 0:

经过

打印('完成申请')