今天早些时候,Josh(一家实习生和博客贡献者)写了一个关于逻辑门的博客帖子。阅读通过Josh的帖子并获得了解那些门的概念和基本功能之后,我现在认为是学习一些代码的完美时间。我将越过每个逻辑门,它的代码verilog.(硬件语言),VHDL.(另一种硬件语言)和C(软件语言)。如果您需要进行硬件语言的复习,您可以阅读Verilog vs. VHDL.。每个门如下所示,其中每个语言的代码在各自的颜色中。

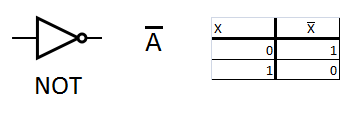

不是:

分配y =〜a;

y <=不是一个;

y =!a;

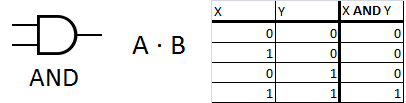

和:

分配y = a&b;

Y <= A和B;

Y = A && B;

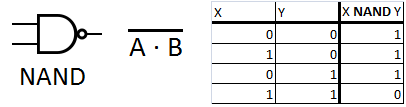

NAND:

分配Y =〜(A&B);

y <= nand b;

Y =!(A && B);

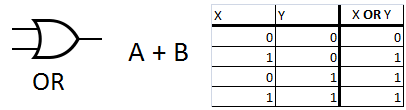

或者:

分配y = a | b;

Y <= A或B;

y = a ||B;

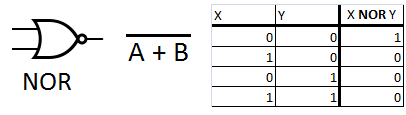

也不:

分配y =〜(a | b);

Y <= A NOR B;

y =!(a || b);

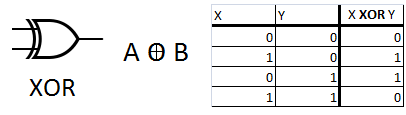

XOR:

分配y = a ^ b;

y <= xor b;

Y =((!a)&& b)||(a &&(!b));

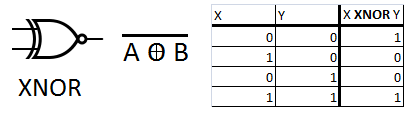

Xnor:

分配y = a ^ b;

Y <= Xnor B;

Y =!((!a)&& b)||(a &&(!b));

您可以从所有这些门的示例中看到,Verilog和VHDL在语法中没有与C不同。实际上,C具有与硬件语言相同的位逻辑运算符。然而,在C的基础操作中不太普遍。不幸的是,C没有XOR和Xnor的符号,因此必须由或不闸门制作。

现在您对FPGA的硬件语言中使用的基本逻辑盖特有了解,请查看FPGA模块在Digilent的学习网站上!

你好,

请修复VHDL代码行

y <=不是一个;

Y <= A和B;

......

y不是VHDL中的Assignmet运算符

请修复表格:

A B |A和B.

---------

......

这将带来表格和图片同步

嗨马丁,

我不确定我的大脑如何交换的差异不如迹象。现在都是固定的。

就像图像一样,我必须努力获得那些固定的,因为他们从另一个帖子中借来。

感谢您的反馈意见!